### **Technical Information**

# High-Speed Digital Test Module R&S TS-PHDT

- For component and board test

- · High pattern rate 40 MHz

- 32 Outputs + 32 Inputs

- Level range -3 V to +10 V, 4 groups

- Hi and Lo programmable, two thresholds

- Memory depth 64 M

- Independent pattern sets, selectively executable and re-usable without new download

- · Tristate at full speed, RTZ clock formatting

- Forbidden-zone detection

- Real-time compare and results: pass/fail, failed channels, failed pattern

- Timing resolution down to 12.5 ns

- Triggering/synchronisation with analog PXI measurement cards

- · Cascading for increased channel count

- · Selftest capabilities

- Soft panel support for immediate deployment

- IVI-C driver support

#### **Product introduction**

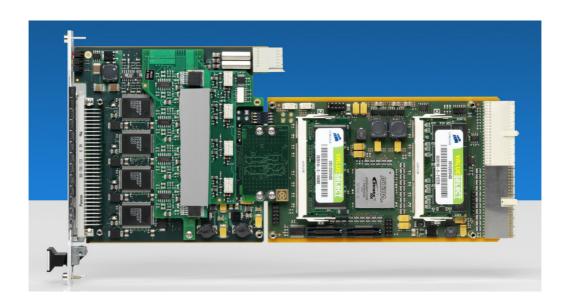

The high-speed digital test module in the R&S CompactTSVP features excellent characteristics in a compact format at a low price. Due to the specifications and the price, the R&S TS-PHDT module can be used both in component and board testing. Its modularity and ability to synchronize with analog modules, e.g. PXI modules, makes mixed signal test possible. For higher channel numbers, several modules can be cascaded.

The R&S TS-PHDT's high pattern rate, timing resolution, and wide level range cover all currently relevant logic families.

Its huge memory capacity of 1.5 GByte makes it possible to create patterns of virtually unlimited length, as they are often generated by simulators. Several pattern sets can be downloaded once and be used again and again, thus eliminating the need for repeated time-consuming reload or download in production. In digital tests, the execution time is not defined by the actual tests

but by the download and upload times. In production, an upload of measured data is not necessary at all. During execution, the hardware locally compares the measured values of the pin electronics – also at maximum pattern rate – with the nominal values in real time. Pass/fail, number of errors, failed channels, failed steps, and a short history are available in the error memory immediately after terminating a pattern set. Uploading larger data volumes is only necessary for debugging during program generation.

The stimulus and measurement unit can be synchronized or used independently of each other. The pattern period and trigger delays can be set with a resolution of up to 12.5 ns; response delay for measurement and auxiliary clock with a resolution up to 3 ns. Clock signals for the device under test (DUT) can be directly generated by means of the auxiliary clock (formatting) and thus do not occupy several steps in the pattern memory for generating a pulse (return-to-zero, RTZ).

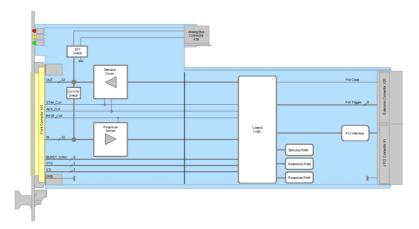

Block diagram of the R&S TS-PHDT module

#### Software support

An IVI-C driver is available for the functions of the High-Speed Digital Test Module R&S TS-PHDT. The driver is a component of the ROHDE & SCHWARZ GTSL software. All functions are

documented extensively in online Help and in the LabWindows/CVI Function Panels.

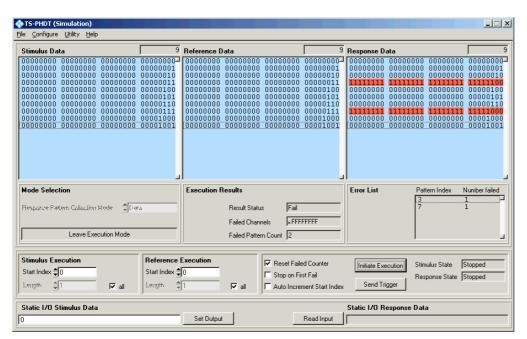

A Soft Panel is available for the module. The Soft Panel is based on the IVI driver and allows for interactive operation of the module.

Soft panel of the R&S TS-PHDT module

## Security by selftest and diagnostic features

A comprehensive dynamic module self test is performed between drivers and sensors and via the analog bus in conjunction with the R&S TS-PSAM module.

Diagnostic LEDs on the module front panel speed up system integration and allow proper operation to be determined at a glance.

#### **Specifications**

Application in R&S TSVP platform

R&S CompactTSVP 1 slot required

Interface

Control bus CompactPCI/PXI

DUT connector (front) DIN 41612, 96 pins

Tolerances for temperature range Temperature coefficient outside 23° ± 5° C ± (0.1 x accuracy) / ° C

#### Data input channels

Channels

32, in 4 ports of 8 channels -3 V to +12 V, clamping if outside range

Input voltage

Input thresholds

Range

Resolution

two per port

-2 V to +9 V

< 1mV (14 bit DAC)

+/- 100 mV for ≤ 3.3 V/ +-150 mV for > 3.3 V, typ

Accuracy Programmable per port Hi and Lo

Hi, Lo, forbidden zone 1 MΩ // 28 pF typ. overvoltage +/- 24 V Detection Input impedance Protection

#### Data output channels

Channels Output voltage Resolution 32, in 4 ports of 8 channels -3 V to +10V < 1mV (14 bit DAC)

Accuracy (static, no load) Output current

+/- 50 mA per channel 500 mA for ≤ 2.9 V/ 200 mA for > 2.9 V Max. current per port

Current limit accuracy per port +/- 40 mA typ.

Programmable per port Rise / fall time (typ) Hi and Lo, current limit 6 ns (20% to 80% of -3 V to 10 V transition)

Tristate control

RTZ clock formatting each channel at max pattern rate static enable for each channel

Output resistance

Protection

39 Ohm typ. short circuit protected, reverse voltage +/- 24 V at 150 mA

#### **Timing generation**

Pattern rate 40 MHz max.

Timing setting ranges

|                | Resolution | Min     | Max  | Condition                      |

|----------------|------------|---------|------|--------------------------------|

| Pattern period | 12.5 ns    | 25 ns   | 10 s |                                |

| Trigger delay  | 12.5 ns    | 0       | 50 s |                                |

| Response delay | 3 ns       | 0       | 10 s | < pattern period               |

| RTZ delay      | 3 ns       | 0       | 10 s | delay + width < pattern period |

| RTZ width      | 3 ns       | 12.5 ns | 10 s | delay + width < pattern period |

Triggering Synchronisation Clock outputs internal, 2 ext, 8 PXI between modules stim, resp, aux (RTZ)

#### Memory

Memory depth

64 M pattern for stim, tristate, ref/mask, resp Pattern comparison real-time or software

Results in real-time

pass/fail, failed channels, failed pattern

count, failed pattern list

#### **General Data**

max. +5 V / 6 A, +12 V / 1.1 A, +3.3 V / 1.5 A Power consumption

from cTSVP frame

compliant with EMC directive 89/336/EEC **EMC** compliance

and EMC standard EN 61326

Safety CE, EN 61010 Part 1

Mechanical loading

Vibration test, sinusoidal 5 Hz to 55 Hz: 2 g, MIL-T-28800D, class 5

55 Hz to 150 Hz: 0.5g, MIL-T-28800D, class 5

10 Hz to 300 Hz, 1.2 g Vibration test, random

Shock test 40g, MIL-STD-810, classes 3 and 5

Temperature loading

Operating temperature range Permissible temperature range Storage temperature range

Humidity

+5°C to +40°C 0 to +50°C -40°C to +70°C

+40°C, 95% rel. humidity

Dimensions Module 316 mm x 174 mm x 20 mm,

Weight 0.6 kg (1.3 lb) Recommended calibration interval not required

#### **Ordering Information**

Test Platform R&S CompactTSVP

Designation High-Speed Digital Test Module

Type Order No. **R&S TS-PHDT** 1157.9704.02 R&S TS-PCA3 1152.2518.02

More information at www.rohde-schwarz.com (search term: TS-PSU)

www.rohde-schwarz.com

Europe: +49 1905 12 4242, outstmersupport@nchde-schwarz.com

USA and Caradix -1-988-879-8792, customersupport@raa-rohde-schwarz.com

A sia: +65 65 130 488, customersupport.asia@rohde-schwarz.com

882° is a ngataral trademat di Baba 8.5 Anvar Cinki 8.0. Traka nama sontrademats di basuwars. Periad in Gimeny Padd 10 1513 1518 17. 1865 il Superiador 10.0. Sapaniar 2018. Oda subsattod rama innationing Subject to change